# cronologic

Ndigo6G-12

User Guide

# **Contents**

| In | Introduction 4                                                |            |  |  |  |

|----|---------------------------------------------------------------|------------|--|--|--|

|    | Features                                                      | 5          |  |  |  |

|    | Board overview                                                | 5          |  |  |  |

|    |                                                               |            |  |  |  |

| 1  | Hardware                                                      | 7          |  |  |  |

|    | 1.1 Installation                                              | 7          |  |  |  |

|    | 1.2 Cooling                                                   | 7          |  |  |  |

|    | 1.3 External Inputs and Connectors                            | 8          |  |  |  |

|    | ·                                                             |            |  |  |  |

|    | 1.3.1 Front bracket inputs                                    | 8          |  |  |  |

|    | 1.3.2 Clock connections                                       | 8          |  |  |  |

|    | 1.3.3 Analog Inputs                                           | 9          |  |  |  |

|    | Analog Offsets                                                | 9          |  |  |  |

|    | AC-Coupling and Baseline Drift                                | 10         |  |  |  |

|    | 1.3.4 Digital TDC Inputs                                      | 10         |  |  |  |

|    | 1.3.5 Digital Control Inputs                                  | 11         |  |  |  |

|    | Use Control Inputs as TDCs                                    |            |  |  |  |

|    | 25c control impacts as 12cs                                   |            |  |  |  |

| 2  | Functionality 1                                               | 12         |  |  |  |

|    | 2.1 ADC Modes                                                 | 12         |  |  |  |

|    | 2.1.1 1-Channel Modes A and D                                 |            |  |  |  |

|    | 2.1.2 2-Channel Mode AD                                       |            |  |  |  |

|    |                                                               |            |  |  |  |

|    | 2.1.3 4-Channel Mode ABCD                                     |            |  |  |  |

|    | 2.1.4 Multiple Sampling Modes                                 |            |  |  |  |

|    | Modes AA and DD                                               | 14         |  |  |  |

|    | Mode AADD                                                     | 14         |  |  |  |

|    | Modes AAAA, DDDD                                              | 15         |  |  |  |

|    | 2.2 Zero Suppression                                          | 15         |  |  |  |

|    | 2.3 Trigger Setup                                             | 16         |  |  |  |

|    |                                                               | 16         |  |  |  |

|    | Analog Inputs                                                 | 16         |  |  |  |

|    | Digital Inputs                                                |            |  |  |  |

|    | 2.3.2 Trigger inputs                                          |            |  |  |  |

|    |                                                               |            |  |  |  |

|    | 2.3.3 Gating trigger events                                   |            |  |  |  |

|    | 2.4 Gating Blocks                                             |            |  |  |  |

|    | 2.4.1 Examples                                                | 22         |  |  |  |

|    | Example 1: Suppression of Noise After Starting an Acquisition | 22         |  |  |  |

|    | 2.4.2 Example 2: Delayed Trigger                              | 23         |  |  |  |

|    | 2.5 Auto Triggering Function Generator                        | 23         |  |  |  |

|    | 2.6 Averaging Mode                                            | 24         |  |  |  |

|    | 2.7 Timing Generator (TiGer)                                  | 24         |  |  |  |

|    | 2.8 Performing a firmware update                              |            |  |  |  |

|    | 2.8.1 Procedure                                               |            |  |  |  |

|    |                                                               |            |  |  |  |

|    | 2.9 Calibrating the TDC                                       |            |  |  |  |

|    | 2.9.1 Re-calibrating the Ndigo6G-12 2                         | 26         |  |  |  |

| 7  | Driver Programming API                                        | 27         |  |  |  |

| 9  | 3.1 Constants                                                 |            |  |  |  |

|    |                                                               |            |  |  |  |

|    | 3.1.1 General                                                 | <i>∠ /</i> |  |  |  |

|   |                  | 3.1.2 Trigger and Gating Block Sources | 28 |  |  |  |

|---|------------------|----------------------------------------|----|--|--|--|

|   |                  | 3.1.3 Function return values           | 29 |  |  |  |

|   |                  | 3.1.4 PCle Information                 | 30 |  |  |  |

|   | 3.2              | Initialization                         |    |  |  |  |

|   |                  | ndigo6g12_get_default_init_parameters  | 32 |  |  |  |

|   |                  | ndigo6g12_init                         |    |  |  |  |

|   |                  | ndigo6g12_close                        |    |  |  |  |

|   |                  | ndigo6g12_device                       |    |  |  |  |

|   |                  | ndigo6g12_init_parameters              |    |  |  |  |

|   | 3.3              | Status information                     |    |  |  |  |

|   | 0.0              | ndigo6g12_get_driver_revision          |    |  |  |  |

|   |                  | ndigo6g12_get_driver_revision_str      |    |  |  |  |

|   |                  | ndigo6g12_count_devices                |    |  |  |  |

|   |                  | ndigo6g12_get_static_info              |    |  |  |  |

|   |                  | ndigo6g12_get_param_info               |    |  |  |  |

|   |                  |                                        |    |  |  |  |

|   |                  | ndigo6g12_get_fast_info                |    |  |  |  |

|   |                  | ndigo6g12_get_pcie_info                |    |  |  |  |

|   |                  | ndigo6g12_param_info                   |    |  |  |  |

|   |                  | ndigo6g12_static_info                  |    |  |  |  |

|   |                  | ndigo6g12_fast_info                    |    |  |  |  |

|   |                  | ndigo6g12_pcie_info                    |    |  |  |  |

|   | 3.4              | Configuration                          |    |  |  |  |

|   |                  | ndigo6g12_get_default_configuration    |    |  |  |  |

|   |                  | ndigo6g12_configure                    |    |  |  |  |

|   |                  | ndigo6g12_configuration                |    |  |  |  |

|   |                  | ndigo6g12_trigger                      |    |  |  |  |

|   |                  | ndigo6g12_trigger_block                | 54 |  |  |  |

|   |                  | ndigo6g12_gating_block                 | 56 |  |  |  |

|   |                  | ndigo6g12_tdc_configuration            | 57 |  |  |  |

|   |                  | ndigo6g12_averager_configuration       | 58 |  |  |  |

|   |                  | ndigo6g12_tdc_channel                  | 59 |  |  |  |

|   |                  | ndigo6g12_tdc_gating_block             | 59 |  |  |  |

|   |                  | ndigo6g12_tdc_tiger_block              | 60 |  |  |  |

|   | 3.5              | Runtime control                        | 62 |  |  |  |

|   |                  | ndigo6g12_start_capture                |    |  |  |  |

|   |                  | ndigo6g12_stop_capture                 |    |  |  |  |

|   |                  | ndigo6g12_manual_trigger               |    |  |  |  |

|   |                  | ndigo6g12_single_shot                  |    |  |  |  |

|   |                  | ndigo6g12_clear_pcie_errors            |    |  |  |  |

|   | 3.6              | Readout                                |    |  |  |  |

|   | 0.0              | ndigo6g12_read                         |    |  |  |  |

|   |                  | ndigo6g12_get_last_error_message       |    |  |  |  |

|   |                  | ndigo6g12_device_state_to_str          |    |  |  |  |

|   |                  | ndigo6g12_read_in                      |    |  |  |  |

|   |                  |                                        |    |  |  |  |

|   |                  | ndigo6g12_read_out                     | 04 |  |  |  |

| 4 | Packet Format 66 |                                        |    |  |  |  |

|   | 4.1              | Output Structure crono_packet          | 66 |  |  |  |

|   |                  | Utility macros                         |    |  |  |  |

|   |                  | Data encoding for ADC hits             |    |  |  |  |

|   |                  | 4.3.1 NDIGO6G12_OUTPUT_MODE_SIGNED16   |    |  |  |  |

|   |                  | 4.3.2 NDIGO6G12_OUTPUT_MODE_RAW        |    |  |  |  |

|   |                  | NOIZ NOIGOUTE_COTTOT_NODE_TWIW         |    |  |  |  |

# Introduction

The Ndigo6G-12 offers 6400 Msps sample rate, 12 bit resolution and a greatly improved readout rate of up to 5200 MB/s.

The unit is a combined ADC/TDC board for the acquisition of pulses in time-of-flight applications. It builds on the established platform of the Ndigo5G-10 but takes it to the next level both in performance and flexibility.

The Ndigo6G-12 was specifically designed for time-of-flight applications like LIDAR or TOF mass spectrometry. A measurement precision of 5 ps (RMS) is achievable for unipolar pulses. In addition, information on the pulse shape, such as area or amplitude, is recorded.

Four channels with 1600 Msps at 12 bit resolution can be acquired independently. Alternatively, the four channels can be combined into two channels or into a single channel. This way, either a higher temporal resolution up to 6400 Msps or a larger dynamic range can be achieved via multiple-sampling modes.

This User Guide documents the hardware and functionality of the Ndigo6G-12 board, as well as the driver programming API provided by the Ndigo6G-12 driver.

This User Guide is also available online at docs.cronologic.de/ndigo6g.

#### **Features**

- · 12 bit dynamic range

- · Up to **6400 Msps** sample rate (in 1-channel mode) for increased resolution in time domain.

- · Up to four ADC channels for your individual measurement setups.

- Four TDC channels with a resolution of 13 ps.

- · Two digital control inputs for effective gating and triggering.

- · PCIe3 x8 interface for simple and fast data transfer to most PCs.

- · Unlimited multihit capabilities.

- Common start and common stop capabilities.

- Continuous ADC readout rate of approx. 5200 MB/s.

- · Zero suppression, significantly reducing PCIe load.

- Internal 10 MHz clock with a time base of 10 ppb or the ability to use an external 10 MHz clock.

# **Board overview**

| Optimized for                      | TOF applications                                                                         |

|------------------------------------|------------------------------------------------------------------------------------------|

| ADC channels                       | 4                                                                                        |

| TDC channels                       | 4                                                                                        |

| Digital control channels           | 2                                                                                        |

| Connectors                         | 10 × LEMO 00                                                                             |

| Sample rate                        | 6400 Msps (1-Channel Mode)<br>3200 Msps (2-Channel Mode)<br>1600 Msps (4-Channel Mode)   |

| Resolution                         | 12 bit                                                                                   |

| Maximum bandwidth                  | TBD                                                                                      |

| TDC bin size                       | 13 ps                                                                                    |

| TDC double pulse resolution        | typically 5 ns                                                                           |

| Multihit                           | unlimited                                                                                |

| Dead time between groups           | none                                                                                     |

| Readout rate                       | 5200 MByte/s (ADC)<br>30 MHits/s (all TDC channels)<br>11.6 MHits/s (single TDC channel) |

| Timestamp range                    | 106 d                                                                                    |

| Readout interface                  | PCle3 x8                                                                                 |

| Time base                          | 10 ppb (internal) or external 10 MHz clock                                               |

| On-board calibration data storage  | yes                                                                                      |

| Adjustable trigger windows         | yes                                                                                      |

| Possibility for overlapping events | yes                                                                                      |

| Easy-to-use Windows C-API          | yes                                                                                      |

| In-system firmware updates         | yes                                                                                      |

# **Hardware**

#### 1.1 Installation

The Ndigo6G-12 board can be installed in any PCle x8 (or higher amount of lanes) PCle slot. If the slot electrically supports less than eight lanes, the board will operate at lower data throughput rates.

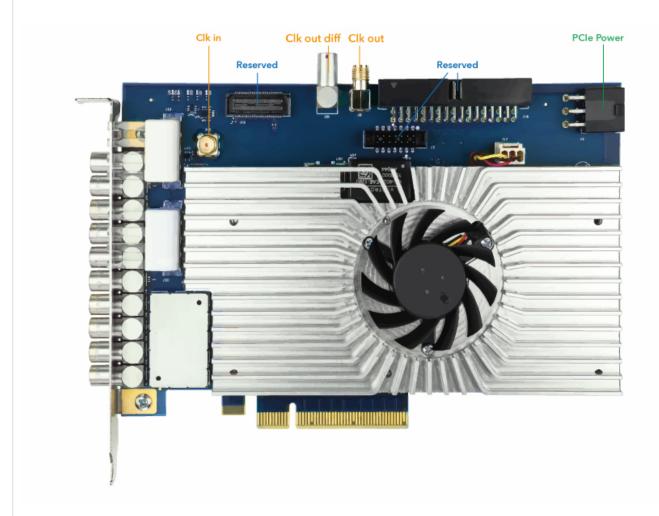

Connect a 6-pin PCIe power cable to the connector at the rear of the board (see Figure 1.1).

# 1 Note

The Ndigo6G-12 does not operate without a 6-pin PCle power connector.

Figure 1.1: Overview of an Ndigo6G-12 board. Note the PCIe power connector at the rear of the board.

#### 1.2 Cooling

The Ndigo6G-12 board is equipped with an active cooling system, ensuring proper cooling of the device. If, however, the temperature of the ADC chip exceeds 90 °C (for instance, if the device is operated in inappropriate environmental conditions, see Section 6.3.1), a warning is issued to the device driver. When the temperature exceeds 95 °C, the ADC chip is disabled to avoid damaging the device.

#### 1.3 **External Inputs and Connectors**

#### 1.3.1 Front bracket inputs

The inputs of the Ndigo6G-12 board are located on the slot bracket.

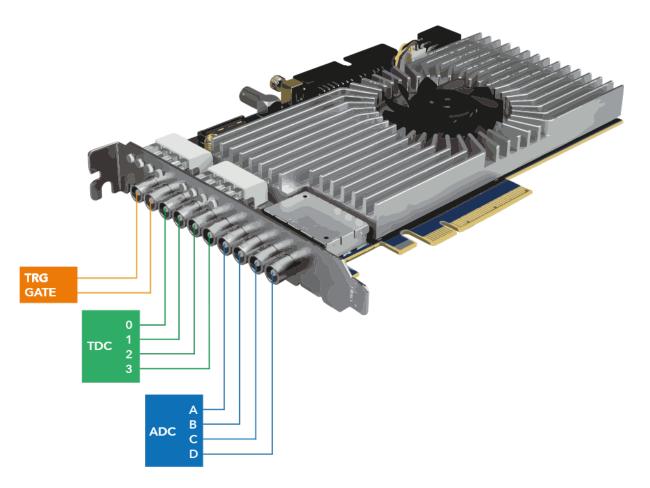

Figure 1.2 shows the location of the four analog inputs A to D (see Section 1.3.3), the four digital TDC inputs 0 to 3 (see Section 1.3.4), and the two digital control inputs TRG and GATE (see Section 1.3.5).

Figure 1.2: Input connectors of an Ndigo6G-12 board located on the PCI bracket.

#### 1.3.2 Clock connections

Connectors to connect an external clock or to access the internal clock signal are located at the top of the board (see Figure 1.1).

#### Clk in (SMA)

Connect your external 10 MHz clock signal here. Make sure to set ndigo6g12\_init\_parameters::clock\_source to NDIGO6G12\_CLOCK\_SOURCE\_SMA.

#### Clk out (SMA)

10 MHz output. This is either the internal clock signal, or an external clock 10 MHz clock if one is used.

## Clk diff (LEMO00)

Same as Clk out, but as a differential signal and with a LEMO00 connector.

## 1.3.3 Analog Inputs

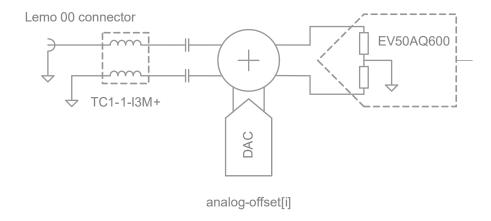

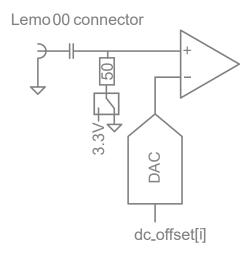

Figure 1.3: Input circuit for each of the four analog channels.

The analog inputs of the ADC are single ended LEMO00 coax connectors. The inputs have a 50  $\Omega$  impedance and are AC coupled. The inputs are converted to a differential signal using a balun.

#### **Analog Offsets**

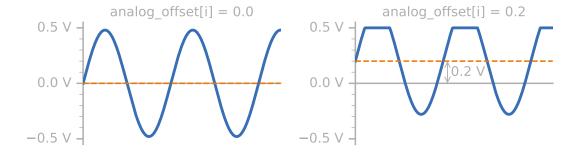

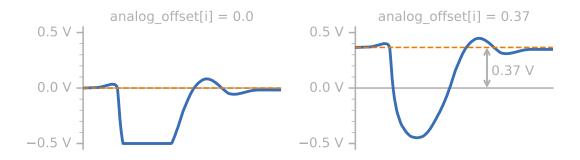

AC coupling removes the DC voltage offset from the input signal. However, users can shift the DC base-line voltage before sampling to a value of their choice (using the <u>analog offset</u> parameter).

This feature is useful for highly asymmetric signals, such as pulses from TOF spectrometers or LIDAR systems. Without analog offset compensation, the pulses would begin in the middle of the ADC range, effectively cutting the dynamic range in half (see Figure 1.5). By shifting the DC baseline to one end of the ADC range, the input range can be used fully, providing the maximum dynamic range. The analog offset can be set between  $\pm$  0.5 V.

Figure 1.4: Users can add an analog offset to the input before sampling.

**Figure 1.5:** Asymmetric signal shifted to increase dynamic range.

#### **AC-Coupling and Baseline Drift**

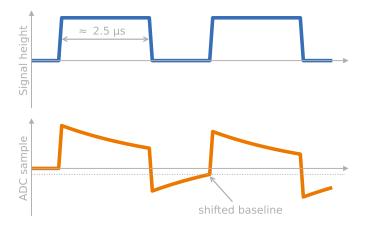

Due to the AC-coupling of the analog and digital inputs, a baseline drift may occur over time (see Figure 1.6). To avoid this problem, make sure your input signal fulfills the requirements laid out in Section 6.3.4.

**Figure 1.6:** Baseline drift due to AC-coupling. A second pulse close to a first may be influenced by a shifted baseline, as sketched in the lower graph.

#### 1.3.4 Digital TDC Inputs

The Ndigo6G-12 board includes four TDC channels with 13 ps timing resolution. The inputs are AC coupled (see Figure 1.7).

**Figure 1.7:** Principal input circuit for each of the digital TDC and control inputs.

The following members of the  $ndigo6g12\_configuration$  struct configure, respectively, TDC channels 0 to 3:

## tdc\_trigger\_offsets[0:3]

Configure the DC offset.

#### trigger[NDIGO6G12\_TRIGGER\_TDC0:NDIGO6G12\_TRIGGER\_TDC3]

Configure if an edge or level trigger is used (relevant, if the TDCs are used in  $trigger\_blocks$  or  $gating\_blocks$ ) and if the rising or falling edge of the input signal triggers.

## tdc\_configuration.channel[0:3]

Configure if (channel [0:3] . enable) and when (channel [0:3] . gating\_block) timestamps

are recorded on the TDC channel.

The trigger unit input logic is summarized, as well, in Figure 2.14.

# 1.3.5 Digital Control Inputs

There are two digital control inputs on the front slot cover called TRG and GATE.

Input-signals on the inputs TRG and GATE are digitized and routed to the Trigger Matrix. They can be used to trigger any of the trigger state machines and gating blocks with maximum sampling rate.

The digital control inputs are optimally suited to be used as digital triggers and gates, and we recommend using them instead of the digital TDC inputs for these purposes.

TRG and GATE are configured analogously to the TDC inputs (see Section 1.3.4 and Figure 2.14), where indices 4 (5) and NDIGO6G12 TRIGGER TRG (NDIGO6G12 TRIGGER GATE) correspond to input TRG (GATE).

The input circuit and trigger logic is identical to the TDC inputs (see Figures 1.7 and 2.14).

#### **Use Control Inputs as TDCs**

The control inputs TRG and GATE can be used as low-resolution TDCs. The dead-time is 5 ns. Pulses should have a width of at least 300 ps to reliably be detected.

To record timestamps with the TRG or GATE input, set config.tdc\_configuration. channel [4/15].enable to true.

#### Note

The digital control inputs TRG and GATE are best suited for triggering and controlling gates.

The digital TDC inputs are best suited for measuring precise time stamps.

# **Functionality**

#### 2.1 ADC Modes

The ADC quantizes the input signal using 12 bits. By default, these are mapped to signed 16 bit (for more details, see Section 4.3).

Data processing such as trigger detection or packet building are always performed at 5 ns intervals. Depending on the ADC mode, this interval may contain 32 (1-Channel Mode @ 6.4 Gsps), 16 (2-Channel Mode @ 3.2 Gsps) or 8 (4-Channel Mode @ 1.6 Gsps) samples.

The ADC mode is configured using ndigo6g12 configuration::adc mode.

The board supports using one, two or four channels. This is configured when the board is initialized, see ndigo6g12\_init\_parameters::application\_type.

During interleaving, the Ndigo6G-12 firmware reorders and groups the data into a linear sample stream. The process is fully transparent. For users, the only difference is that a 5 ns cycle can contain 8, 16 or 32 samples, depending on the mode.

Depending on the application type, the minimal length of the output packets changes. The minimal lengths are:

- $\cdot$  3  $\times$  32 Samples (15 ns) @ 6.4 Gsps (1-Channel Mode)

- $\cdot$  3 × 16 Samples (15 ns) @ 3.2 Gsps (2-Channel Mode)

- $\cdot$  4 × 8 Samples (20 ns) @ 1.6 Gsps (4-Channel Mode)

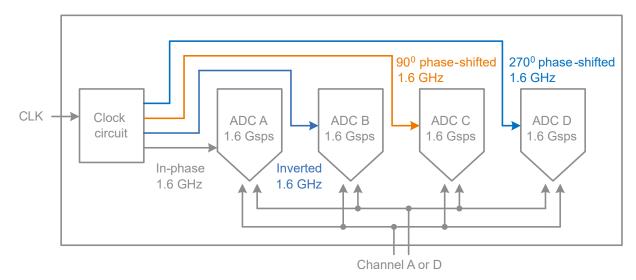

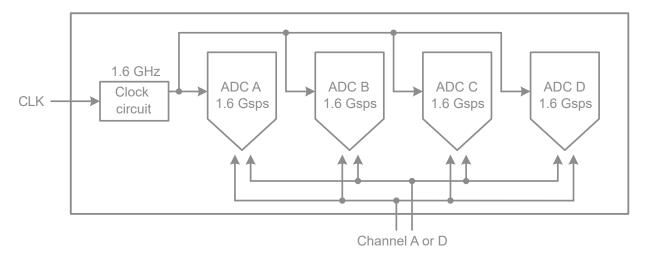

#### 2.1.1 1-Channel Modes A and D

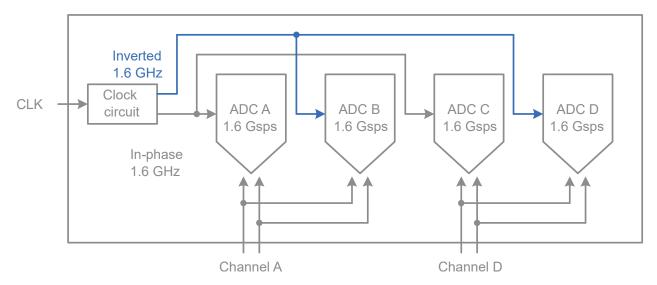

In these modes, only a single channel is used. The analog signal on that channel is digitized at 6.4 Gsps. Packet size is always a multiple of 32 samples per 5 ns (See Figures 2.1 and 2.12).

For this mode, ndigo6g12 static info::application type needs to be either NDIGO6G12 APP TYPE 1CH or NDIGO6G12 APP TYPE AVRG.

Figure 2.1: ADCs in 1-channel-mode A, B, C or D interleaved for 6.4 Gsps.

#### 2.1.2 2-Channel Mode AD

In this mode, two channels are used simultaneously. The analog signals on these channels are digitized at 3.2 Gsps each. Packet size is always a multiple of 16 samples per 5 ns (See Figures 2.2 and 2.11).

For this mode,  $ndigo6g12\_static\_info::application\_type$  needs to be  $NDIGO6G12\_APP\_TYPE\_2CH$ .

Figure 2.2: ADCs in 2-channel-mode AD, interleaved for 3.2 Gsps.

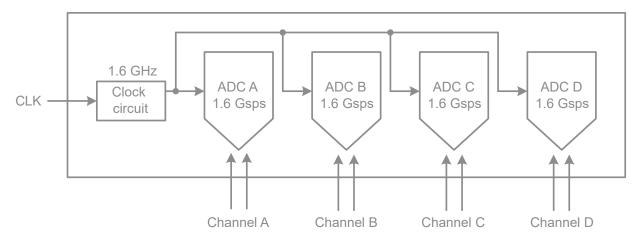

#### 2.1.3 4-Channel Mode ABCD

In this mode, all four channels are digitized independently at 1.6 Gsps each. The packet size is always a multiple of 16 samples per 10 ns. (See Figures 2.3 and 2.10).

For this mode,  $ndigo6g12\_static\_info::application\_type$  needs to be  $NDIGO6G12\_APP\_TYPE\_4CH$ .

Figure 2.3: ADCs in 4-channel-mode ABCD at 1.6 Gsps.

#### 2.1.4 Multiple Sampling Modes

In these modes, only the specified input channels are used, but the channels are sampled independently by the ADC cores. The output of the board depends on  $ndigo6g12\_configuration::sample\_averaging$ .

• sample\_averaging == false: The digitized samples are output as separate packets (the number of which depends on the selected mode).

• sample\_averaging == true: The average of the digitized samples is calculated and output as one single packet.

Using the same trigger settings on all ADCs can be used to reduce noise by averaging the four channels. To deal with complex triggering conditions, different trigger settings on each of the ADCs can be used.

The Ndigo6G-12 provides four ADCs sampling at 1.6 Gsps each. Higher speed modes are implemented by interleaving two or four of these ADCs.

#### **Modes AA and DD**

In this mode, input channel A (or D) is sampled at 3.2 Gsps two times and independently by the internal ADC cores, see Figure 2.4.

For this mode,  $ndigo6g12\_static\_info::application\_type$  needs to be NDIGO6G12\_APP\_TYPE\_2CH.

Figure 2.4: ADCs in 2-channel-mode AA or DD at 3.2 Gsps.

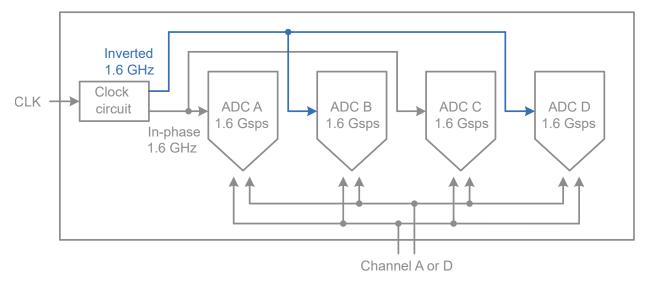

#### **Mode AADD**

In this mode, input channel A and D are sampled at 1.6 Gsps two times and independently by the internal ADC cores, see Figure 2.5.

For this mode,  $ndigo6g12\_static\_info::application\_type$  needs to be NDIGO6G12 APP TYPE 4CH.

Figure 2.5: ADCs in 4-channel-mode AADD at 1.6 Gsps.

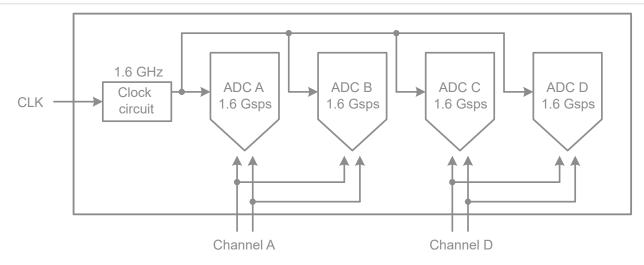

#### Modes AAAA, DDDD

In this mode, input channel A (or D) are sampled at 1.6 Gsps four times and independently by the internal ADC cores, see Figure 2.6.

For this mode,  $ndigo6g12\_static\_info::application\_type$  needs to be NDIGO6G12 APP TYPE 4CH.

Figure 2.6: ADCs in 4-channel-mode AAAA or DDDD at 1.6 Gsps.

# 2.2 Zero Suppression

One of the Ndigo6G-12's key features is on-board zero suppression to reduce PCIe bus load. Only data that passes specifications predefined by the user is transmitted. Data is transmitted as so-called "packets." For the ADC channels, the packet contains the waveform data and a timestamp giving the absolute time (i.e., the time since the start of the data acquisition) of the packet's first sample.

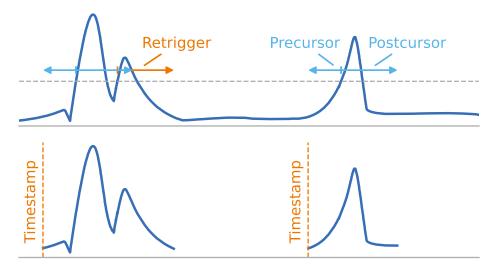

Figure 2.7 shows a simple example: Data is only written to the PC if the sample values exceed a specific threshold. Expanding on that, the Ndigo6G-12's zero suppression can be used to realize much more complex scenarios using the Trigger and Gating Blocks (see Sections 2.3 and 2.4).

Figure 2.7: Simple zero suppression: Only data with values above a threshold are written to the PC.

#### **Trigger Setup** 2.3

The Ndigo6G-12 records analog waveforms using zero suppression. Whenever a relevant waveform is detected, data is written to an internal FIFO memory.

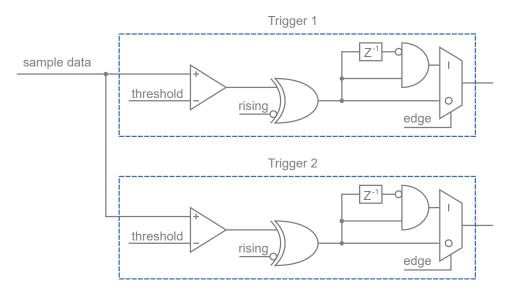

Each ADC channel has two trigger units. These can be configured independently (e.g., one unit could trigger on rising edges, the other on falling). They are configured with config. trigger.

Each ADC channel has a corresponding trigger block that determines whether data is written to the internal FIFOs. The trigger blocks are configured with config. trigger\_block. Each trigger block can take any amount of trigger units as a source (for details, see ndigo6g12\_trigger\_block::sources or Section 2.3.2), thus, enabling sophisticated trigger setups.

#### 2.3.1 Trigger configuration

#### **Analog Inputs**

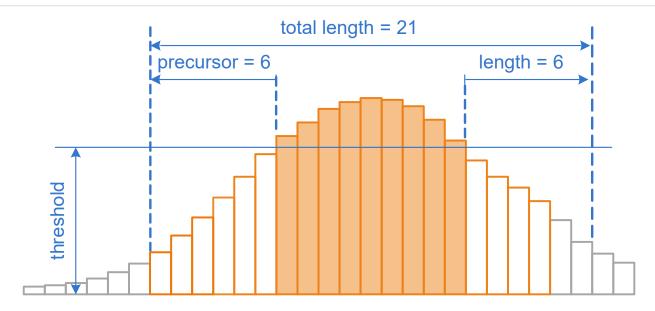

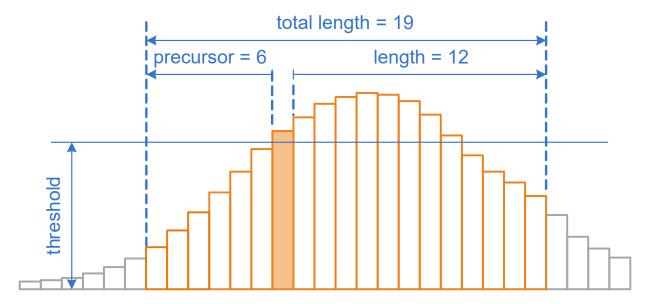

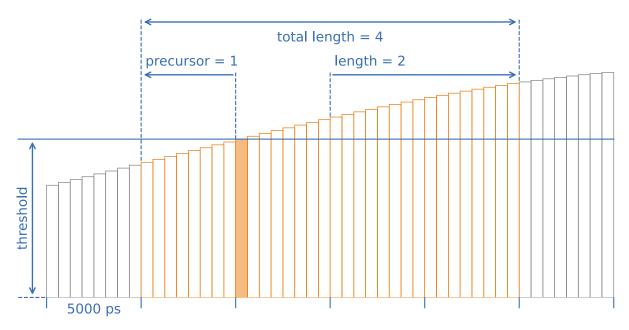

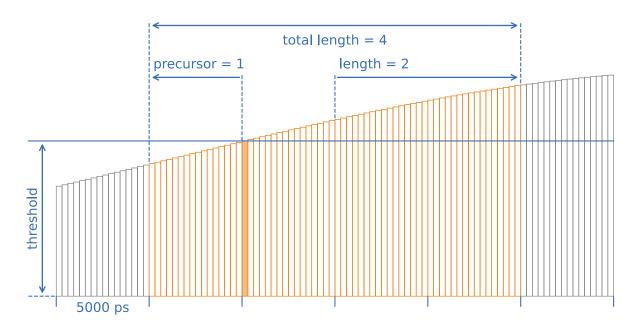

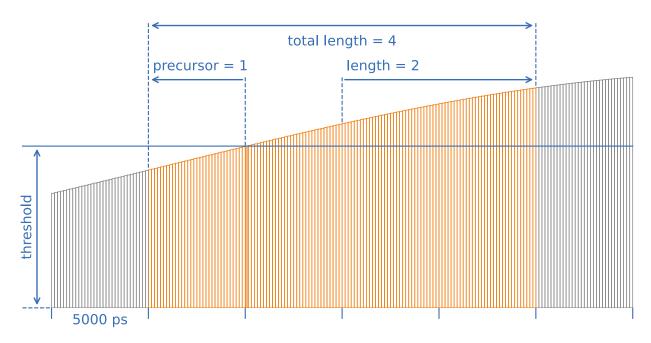

Users can specify a *threshold* and can choose whether triggering is used whenever incoming data is below or above the threshold (level triggering, see Figure 2.8) or only if data exceeds the threshold (edge triggering, see Figure 2.9).

A gate length can be set to extend the recording window by multiples of 5 ns. Furthermore, a precursor window can be specified, causing the trigger unit to write data to the FIFO (precursor  $\times$  5 ns) before the trigger event.

When edge triggering is used, all packets have the same length of (precursor + length + 1)-cycles of 5 ns. For level triggering, packet length is data dependent.

If retrigger is enabled and the trigger conditions are fulfilled during the recording of the postcursor, the recording window is extended (see Figure 2.7).

Figure 2.8: Example for level triggering.

Figure 2.9: Example for edge triggering.

Figure 2.10: Triggering in 4-channel mode at 8 samples per clock cycle.

Figure 2.11: Triggering in 2-channel mode at 16 samples per clock cycle.

Figure 2.12: Triggering in 1-channel mode at 32 samples per clock cycle.

#### **Digital Inputs**

For all digital inputs, the configuration value ndigo6g12 trigger::threshold is ignored. Their trigger threshold is configured by ndigo6g12\_configuration::tdc\_trigger\_offsets.

Equivalently to the analog inputs, edge- or level-trigger functionality can be enabled using ndigo6g12\_trigger::edge. The duration of a level trigger is solely limited by the AC-coupling (see Figure 1.6 for the effects of AC-coupling on a signal).

# 2.3.2 Trigger inputs

A trigger block can use several input sources:

- The eight trigger decision units of all four ADC channels (Figure 2.13)

- The four TDC and the two digital control inputs (Figure 2.14)

- · A function trigger providing random or periodic triggering (see Auto Triggering Function Generator).

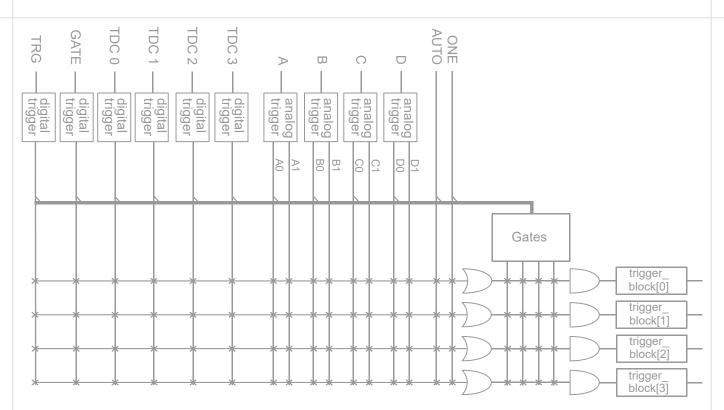

Trigger inputs from the above sources can be concatenated using a logical OR by setting the appropriate bits in the bitmask (see <a href="mailto:ndigo6g12\_trigger\_block::sources">ndigo6g12\_trigger\_block::sources</a>).

See also Figure 2.15.

Figure 2.13: From the ADC inputs, a trigger unit creates an input flag for the trigger matrix. Each digitizer channel (A, B, C, D) has two trigger units.

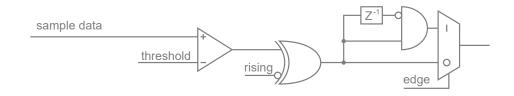

Figure 2.14: The digital inputs TDC0, TDC1, TDC2, TDC3, TRG, and GATE have simpler trigger units.

Figure 2.15: Trigger Matrix. The eight trigger signals from the four analog channels and the trigger signals from the six digital channels (four TDC channels, TRG, GATE) can be combined to create a trigger input for each trigger block. Additionally, four gate signals (see Figure 2.16) can be used to suppress trigger during configurable time frames.

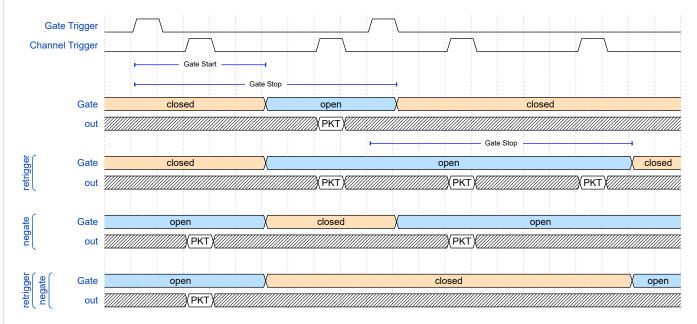

## 2.3.3 Gating trigger events

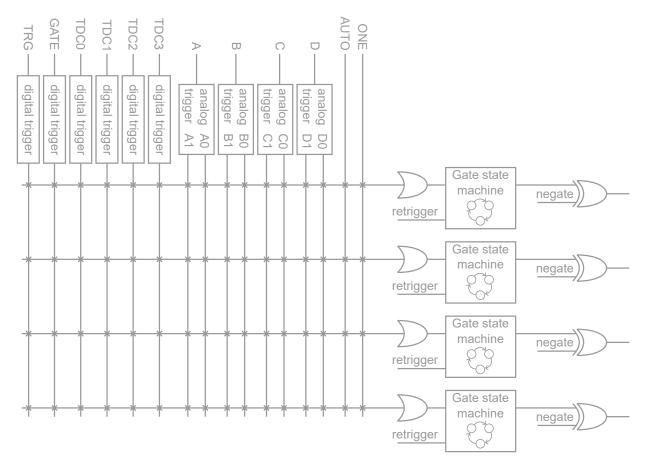

Triggers can be fed into the  $gating\_blocks$  as outlined in Chapter 2.4 and Figure 2.16.

In return, the gating\_blocks can be used to block writing data to the FIFO. That way, only zero-suppressed data occurring when the selected gate is active is transmitted. This procedure reduces PCIe bus load even further.

Which gating block is used to block a particular trigger block is configured with ndigo6g12\_trigger\_block::gates.

# 2.4 Gating Blocks

In order to decrease the amount of data transmitted to the PC, the Ndigo6G-12 includes four independent gate and delay units.

They are configured using  $ndigo6g12\_configuration::gating\_block$  and (specifically for the TDC channels) ndigo6g12\_tdc\_channel::gating\_block.

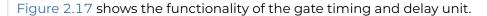

A gate and delay unit creates a gate window starting and closing at specified times after a trigger event (as configured by the user with  $ndigo6g12\_gating\_block::start$  and stop).

Concretely, if a trigger event is detected, a timer starts. After the timer reaches the time corresponding to start, the gate will activate. After the timer reaches the time corresponding to stop, it will inactivate.

This behavior may be influenced by the retrigger feature. With this feature enabled, another trigger signal will reset the timer to zero. That means, if a second trigger is detected before the gate is activated,

Figure 2.16: Gating Blocks: Each gating block can use an arbitrary combination of inputs to trigger its state machine. The outputs can be individually inverted and routed to the AND-gate feeding the trigger blocks.

the time until it activates is extended. If, however, the gate was already active, the time until it inactivates will be extended.

#### Attention

A bug in Firmware Rev.  $\leq 1.24120$  causes the retrigger feature to reset the gate logic entirely (i.e, the state of the gate will inactivate after a retrigger event).

Depending on  $ndigo6g12\_gating\_block::negate$ , an active gate will be open (signal detection enabled) or closed (signal detection disabled).

Each gating block can use an arbitrary combination of inputs which trigger it. This is configured using ndigo6g12 gating block::sources.

trigger blocks can use the gate signal to suppress data acquisition, that is, only data that fulfills zero suppression specifications occurring in an open gate window is written to the PC.

Figure 2.17: Gate and delay functionality: When a trigger occurs, the gate opens after a set period of time "Gate Start" and closes when it reaches "Gate Stop". A second trigger event may influence this behavior if retriggering is enabled.

#### 2.4.1 Examples

#### **Example 1: Suppression of Noise After Starting an Acquisition**

In mass spectrometer and other experiments, noise while starting data acquisition can result in undesired trigger events during start-up time. To prevent noise in the output data, a gating block could be used to suppress all triggers during start-up.

The following example illustrates the use of a gating block (in the following,  $gating \ block[0]$ ) to prevent recording noise:

· Set up the GATE input to trigger on each acquisition start, that is,  $trigger[NDIG06G12\_TRIG-$ GER\_GATE] is configured corresponding to the input signal (e.g., configuring the polarity).

- NDIG06G12 TRIGGER SOURCE GATE is selected as input source of gating block[0].source and the  $gating \ block[0]$ . start parameter is set to 0.

- The gating block[0]. stop parameter is set to the desired length (in multiples of 5 ns).

- gating\_block[0].negate is set to true.

Now, gating\_block[0] will output a LOW pulse of the desired length (that is, the gate is closed during start-up time) whenever there is a pulse on the GATE input.

Now, select the above gate for the trigger bock you want to use for triggering data acquisition, e.g., trigger block[0]:

Set trigger block[0].sources e.g.,

```

config.trigger_block[0].sources = NDIGO6G12_TRIGGER_SOURCE_AO | NDIGO6G12_

TRIGGER SOURCE DO

```

uses the ADC input channels A and D as sources.

Set NDIGO6G12\_TRIGGER\_GATE\_0 as trigger\_block[0].gates.

```

config.trigger block[0].gates = NDIGO6G12 TRIGGER GATE 0

```

Now, recording of data is suppressed for an initial start-up time.

#### 2.4.2 Example 2: Delayed Trigger

To sample a short window at a specified time after a trigger event on a channel, a gating block can be used to create a delayed trigger. To do this, one of the triggers of the channel of interest is configured to the desired parameters by selecting the threshold, setting the edge polarity and enabling edge triggering.

Instead of directly using this trigger as an input to the trigger block's input matrix, the trigger is selected as an input to a gating block. The block is configured with start = delay (in multiples 5 ns) and stop = start+1, negate = false. This causes the gating block to produce a one clock cycle pulse on its output after the specified delay.

To send this pulse to the trigger block, the gating block must be enabled in the trigger block's AND matrix and the ONE trigger source must be selected.

#### 2.5 **Auto Triggering Function Generator**

Some applications require periodic or random triggering. The Ndigo6G-12's function generator provides this functionality.

The delay between two trigger pulses of this trigger generator is the sum of two components: A fixed value M and a pseudo-random value given by the exponent N.

The period is

$$T = M + [1...2^N] - 1$$

clock cycles with a duration of 5 ns per cycle, where  $6 \le M < 2^{32}$  and  $0 \le M < 32$ .

This allows to monitor input signals at times the current trigger configuration does not trigger, e.g., to get baseline information in mass spectrometry applications. It can also be used to determine a suitable threshold level for the trigger by first getting random statistics on the input signal.

This functionality is enabled and configured using ndigo6g12 configuration::auto trigger period and auto trigger random exponent.

# 2.6 Averaging Mode

Instead of streaming each recorded trigger event as packets, it is possible to average over multiple trigger events.

By initializing the Ndigo6G-12 board with NDIGO6G12\_APP\_TYPE\_AVRG, Averaging Mode is enabled. Then, a number of ndigo6g12\_averager\_configuration::iterations are averaged before output is written.

Averaging Mode can be used only with ADC modes A and D (see Section 2.1).

#### Attention

Be aware that in averaging mode, the first two 64-bit words in data are an extended header. See Section 4.5 for more information.

# **Timing Generator (TiGer)**

The LEMO connectors of all TDC channels, the TRG channel, and the GATE channel can be used as an AC-coupled trigger output. The TiGer functionality can be configured independently for each connector.

Each TiGer is configured using the ndigo6g12\_tdc\_tiger\_block struct. The tiger blocks can be triggered by any combination of inputs, including the auto-trigger and the ADC channels.

#### Note

The TiGer configuration is similar to the gating blocks.

The TiGer can be used in different output modes. For an overview of the different modes, see the documentation in the API section.

With restrictions, the respective LEMO connectors can be used simultaneously as a TiGer output and as an input.

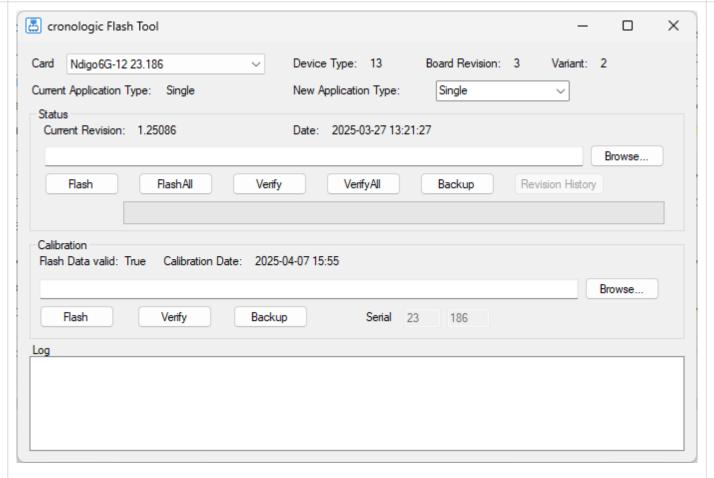

# Performing a firmware update

The Ndigo6G-12 device driver includes the tool FirmwareGUI\_64.exe. It can be used to perform a firmware update.

The tool is located in your device driver installation path under apps x64.

The tool is shown in Figure 2.18.

Figure 2.18: Firmware flash tool for the Ndigo6G-12.

#### 2.8.1 Procedure

- 1. If you have multiple Ndigo6G-12 installed, choose a card in the "Card" dropdown menu.

- 2. It is advisable to perform a backup of the current firmware and calibration data. Click the respective "Backup" button in the tool.

- 3. Optionally select the application type that you wish to use. This step is not required and can also be performed when configuring the Ndigo6G-12 in your user software.

- 4. Browse to the new firmware file: In the "Status" section, click on "Browse". The firmware that is delivered with the device driver is located at firmware\Ndigo6G\_Firmware\_YYYYMMDD.cronorom.

- 5. Optionally compare the currently installed firmware with the selected firmware by pressing "Verify".

- 6. Click "Flash" to perform the firmware update.

#### Attention

The new firmware will only be used after a *complete* power cycle. A simple reboot may not be sufficient.

### Attention

After a firmware update the TDCs have to be re-calibrated. See *Calibrating the TDC* for the procedure.

#### 2.9 Calibrating the TDC

You can backup or restore the calibration from a previous backup using FirmwareGUI\_64.exe (see Performing a firmware update and Figure 2.18).

In the "Calibration" section, click "Backup" and choose a location for the .ndigo6gcal calibration file.

You can compare the currently used calibration with the calibration from a backup file by clicking "Verify" button after browsing to your calibration file.

You can flash the calibration from a \*.ndigo6gcal file onto the Ndigo6G-12 by clicking "Flash" after browsing to your calibration file.

#### Attention

After performing a *firmware update*, it is always necessary to re-calibrate your Ndigo6G-12. Restoring a previous calibration from a backup is not sufficient.

## 2.9.1 Re-calibrating the Ndigo6G-12

Calibration is performed with the command-line tool ndigo6g12\_tdc\_alignment.exe. It is located in the installation directory of the Ndigo6G-12 driver under apps\x64 (by default C:\Program Files\ cronologic\Ndigo6G-12\apps\x64).

Navigate to the folder and open it in a terminal, then start the tool from that terminal.

The tool takes command line arguments. Run .\ndigo6g12 tdc alignment.exe -help for an overview.

Calibration is performed by simply starting the tool: .\ndigo6g12 tdc alignment.exe.

If multiple Ndigo6G-12 are installed in your system, you can perform calibration for each one of them by calling .\ndigo6g12\_tdc\_alignment.exe -index <device\_index>, where the <device\_index> starts at 0 and increments for each Ndigo6G-12.

# **Driver Programming API**

#### Attention

The API requires *driver versions* >2.0.0 and *firmware* 1.24120.

The API is a DLL with C linkage. Declarations of the interface are found in  $ndigo6g12\_interface.h$ , provided by the Ndigo6G-12 driver.

This chapter provides an overview of the provided API functionality.

#### 3.1 Constants

#### 3.1.1 General

## NDIGO6G12\_API\_VERSION

The current API version.

#### NDIGO6G12\_TRIGGER\_COUNT

The number of ADC and TDC triggers, including AUTO and ONE.

#### NDIGO6G12\_ADC\_CHANNEL\_COUNT

The number of analog input channels.

## NDIGO6G12\_GATE\_COUNT

The number of gating blocks.

#### NDIGO6G12\_TDC\_CHANNEL\_COUNT

The number of high (TDC0-3) and low (TRG, GATE) resolution TDC input channels.

#### NDIGO6G12\_BITSTREAM\_DATE\_LEN

Bitstream date format: YYYY-MM-DD hh:mm:ss

#### NDIGO6G12\_CALIBRATION\_DATE\_LEN

Calibration date format: YYYY-MM-DD hh:mm

#### NDIGO6G12\_FLASH\_SIG\_LEN

Length of Ndigo6G-12 flash signature

#### NDIGO6G12\_FIFO\_DEPTH

ADC sample FIFO depth.

It is the maximum recording length in multiples of 5 ns.

#### NDIGO6G12\_MAX\_PRECURSOR

Maximum for ndigo6g12\_trigger\_block::precursor.

#### NDIGO6G12\_MAX\_MULTISHOT

Maximum for ndigo6g12\_trigger\_block::multi\_shot\_count.

## 3.1.2 Trigger and Gating Block Sources

Bitmasks for trigger sources.

Used for ndigo6g12\_trigger\_block::sources, ndigo6g12\_gating\_block::sources, ndigo6g12\_tdc\_gating\_block::sources, and ndigo6g12\_tdc\_tiger\_block::sources.

#### **Defines**

#### NDIGO6G12\_TRIGGER\_SOURCE\_NONE

All trigger sources disabled.

NDIGO6G12\_TRIGGER\_SOURCE\_AO

NDIGO6G12\_TRIGGER\_SOURCE\_A1

NDIGO6G12\_TRIGGER\_SOURCE\_BO

NDIGO6G12\_TRIGGER\_SOURCE\_B1

NDIGO6G12\_TRIGGER\_SOURCE\_CO

NDIGO6G12\_TRIGGER\_SOURCE\_C1

NDIGO6G12\_TRIGGER\_SOURCE\_DO

NDIGO6G12\_TRIGGER\_SOURCE\_D1

NDIGO6G12\_TRIGGER\_SOURCE\_TDCO

NDIGO6G12\_TRIGGER\_SOURCE\_TDC1

NDIGO6G12\_TRIGGER\_SOURCE\_TDC2

NDIGO6G12\_TRIGGER\_SOURCE\_TDC3

NDIGO6G12\_TRIGGER\_SOURCE\_TRG

NDIGO6G12\_TRIGGER\_SOURCE\_GATE

NDIGO6G12\_TRIGGER\_SOURCE\_AUTO

NDIGO6G12\_TRIGGER\_SOURCE\_ONE

Trigger signal is active each clock cycle.

NDIGO6G12\_TRIGGER\_SOURCE\_FPGAO

Deprecated. Alias for NDIGO6G12\_TRIGGER\_SOURCE\_TRG.

NDIGO6G12\_TRIGGER\_SOURCE\_FPGA1

Deprecated. Alias for NDIGO6G12\_TRIGGER\_SOURCE\_GATE.

#### 3.1.3 Function return values

Return codes of various functions.

All ERRORS must be positive integers, because the upper byte is used by crono\_tools

**Defines**

CRONO\_OK

CRONO\_WINDRIVER\_NOT\_FOUND

CRONO\_DEVICE\_NOT\_FOUND

CRONO\_NOT\_INITIALIZED

CRONO\_WRONG\_STATE

CRONO\_INVALID\_DEVICE

CRONO\_BUFFER\_ALLOC\_FAILED

CRONO\_TDC\_NO\_EDGE\_FOUND

CRONO\_INVALID\_BUFFER\_PARAMETERS

CRONO\_INVALID\_CONFIG\_PARAMETERS

CRONO\_WINDOW\_CALIBRATION\_FAILED

CRONO\_HARDWARE\_FAILURE

CRONO\_INVALID\_ADC\_MODE

CRONO\_SYNCHRONIZATION\_FAILED

CRONO\_DEVICE\_OPEN\_FAILED

CRONO\_INTERNAL\_ERROR

CRONO\_CALIBRATION\_FAILURE

CRONO\_INVALID\_ARGUMENTS

CRONO\_INSUFFICIENT\_DATA

#### 3.1.4 PCle Information

PCIe correctable error flags.

Only relevant when troubleshooting.

#### **Defines**

CRONO\_PCIE\_RX\_ERROR

CRONO\_PCIE\_BAD\_TLP

CRONO\_PCIE\_BAD\_DLLP

CRONO\_PCIE\_REPLAY\_NUM\_ROLLOVER

CRONO\_PCIE\_REPLAY\_TIMER\_TIMEOUT

CRONO\_PCIE\_ADVISORY\_NON\_FATAL

CRONO\_PCIE\_CORRECTED\_INTERNAL\_ERROR

CRONO\_PCIE\_HEADER\_LOG\_OVERFLOW

PCIe uncorrectable error flags.

Only relevant when troubleshooting.

#### **Defines**

```

CRONO_PCIE_UNC_UNDEFINED

CRONO_PCIE_UNC_DATA_LINK_PROTOCOL_ERROR

CRONO_PCIE_UNC_SURPRISE_DOWN_ERROR

CRONO_PCIE_UNC_POISONED_TLP

CRONO_PCIE_UNC_FLOW_CONTROL_PROTOCOL_ERROR

CRONO_PCIE_UNC_COMPLETION_TIMEOUT

CRONO_PCIE_UNC_COMPLETER_ABORT

CRONO_PCIE_UNC_UNEXPECTED_COMPLETION

CRONO_PCIE_UNC_RECEIVER_OVERFLOW_ERROR

CRONO_PCIE_UNC_MALFORMED_TLP

CRONO_PCIE_UNC_ECRC_ERROR

CRONO_PCIE_UNC_UNSUPPORED_REQUEST_ERROR

```

#### 3.2 Initialization

To use a Ndigo6G-12 board, it first needs to be initialized. This is done by calling  $ndigo6g12\_init()$ . The initialization parameters necessary for ndigo6g12 init() are provided in the ndigo6g12 init parameters struct.

The general procedure for initialization is as follows:

- 1. Load a default set of initialization parameters using <a href="mailto:ndigo6g12\_get\_default\_init\_parame-">ndigo6g12\_get\_default\_init\_parame-</a> ters.

- 2. If necessary, adjust default parameters to your specific needs.

- 3. Initialize the Ndigo6G-12 board using ndigo6g12\_init().

- 4. Check that the initialization was successful. If so, the return value of  $ndigo6g12\_init()$  is CRONO OK.

Information on the current device will be stored as type ndigo6g12 device.

```

ndigo6g12_get_default_init_parameters(init)

```

Macro that calls <code>ndigo6g12\_get\_default\_init\_parameters\_version</code> with the correct API version.

int ndigo6g12\_get\_default\_init\_parameters\_version(ndigo6g12\_init\_parameters\*init, int client\_api\_version)

Sets up the standard parameters.

Gets a set of default parameters for ndigo6g12\_init(). This must always be used to initialize the ndigo6g12\_init\_parameters structure.

For convinience, the macro ndigo6g12\_get\_default\_init\_parameters is provided, which automatically sets the correct client api version.

#### Default values:

- card\_index = 0

- board\_id = 0

- buffer\_size[0] = 64 (MiB)

- buffer\_size[1-7] = 0 (unused)

- dma\_read\_delay = 1000

- perf\_derating = 0

- led\_flashing\_mode = 1

- clock\_source = NDIGO6G12\_CLOCK\_SOURCE\_INTERNAL

- application\_type = NDIGO6G12\_APP\_TYPE\_CURRENT

- force\_bitstream\_update = false

- partial\_bitstream\_size = 0

- partial\_bitstream = nullptr

- firmware\_locations = nullptr

#### **Parameters**

- init [in] Pointer to a structure in which to store the initialization values.

- · client\_api\_version [in] NDIGO6G12\_API\_VERSION

#### Returns

See Function return values.

int ndigo6g12\_init(ndigo6g12\_device \*device, ndigo6g12\_init\_parameters \*params, const char \*\*error\_message)

Open and initialize an Ndigo6G-12 board.

Which Ndigo6G-12 board will be initialized is determined by ndigo6g12\_init\_parameters::card\_index.

#### **Parameters**

device – [out] Pointer to the device struct.

- · params [in] Pointer to the structure that contains the initialization parame-

- error\_message [out] Location in which to store the error message as plain

#### **Returns**

See Function return values.

## int ndigo6g12\_close(ndigo6g12\_device \*device)

Finalize the driver for this device.

#### **Parameters**

device - [in] Pointer to the device that should be finalized.

#### **Returns**

See Function return values.

#### struct ndigo6g12\_device

Contains information of the Ndigo6G-12 device in use.

#### **Public Members**

bool is\_valid

void \*ndigo6g12

#### struct ndigo6g12\_init\_parameters

Struct for the initialization of the Ndigo6G-12.

This structure MUST be completely initialized.

#### **Public Members**

#### int version

The version number.

It is increased when the definition of the structure is changed. The increment can be larger than 1 to match driver version numbers or similar. Set to 0 for all versions up to first release.

Must be set to NDIGO6G12\_API\_VERSION.

#### int card\_index

The index in the list of Ndigo6G-12 boards that should be initialized.

There might be multiple boards installed in the system that are handled by this driver as reported by ndigo6g12\_count\_devices(). This index selects one of them. Boards are enumerated depending on the PCIe slot. The lower the bus number and the lower the slot number the lower the card index.

#### int board\_id

The global index in the list of all cronologic devices.

This 8-bit number is filled into each packet created by the board and is useful if data-streams of multiple boards will be merged. If only Ndigo6G-12 boards are used, this number can be set to card\_index. If boards of different types that use a compatible data format are used in a system, each board should get a unique ID.

## int64\_t buffer\_size[8]

The minimum size of the DMA buffer.

If set to 0, the default size of 64 MiBytes is used. For the Ndigo6G-12 only the first entry is used.

#### int dma\_read\_delay

The update delay of the writing pointer after a packet has been send over PCIe.

Default is 1000. Do not change.

#### int perf\_derating

Default 0, corresponding to 1.6, 3.2, or 6.4 Gsps (depending on application\_type).

For internal use only. Do not change.

#### int led\_flashing\_mode

Controls the LED flashing mode.

Define what LEDs do during initialization:

- · 0: LEDs are off

- · 1: LEDs light up once

#### int clock\_source

Defines which clock source is used (internal, SMA, AUX2).

Must be one of the following:

#### NDIGO6G12\_CLOCK\_SOURCE\_INTERNAL

Device is using the internal 10 MHz clock.

#### NDIGO6G12\_CLOCK\_SOURCE\_SMA

Use an external 10 MHz clock as reference. The input is the SMA socket located on the board.

### NDIGO6G12\_CLOCK\_SOURCE\_AUX2

Use an external 10 MHz clock as reference. The input is the TRG LEMO connector located on the slot bracket.

#### uint32\_t application\_type

Select the application type.

Note that ndigo6g12\_configuration::adc\_mode must match the application type chosen here.

Must be one of the following:

#### NDIGO6G12\_APP\_TYPE\_AVRG

Averaging mode at 6.4 Gsps.

For more information, see Section 2.6.

#### NDIGO6G12\_APP\_TYPE\_4CH

Four ADC channels at 1.6 Gsps.

#### NDIGO6G12\_APP\_TYPE\_2CH

Two ADC channels at 3.2 Gsps.

#### NDIGO6G12\_APP\_TYPE\_1CH

One ADC channel at 6.4 Gsps.

## NDIGO6G12\_APP\_TYPE\_CURRENT

Use currently installed application type.

#### crono\_bool\_t force\_bitstream\_update

Force a bitstream update that configures the FPGA.

During the initialization of the board, a bitstream configures the FPGA of the Ndigo6G-12. This is only done if during the initialization of the Ndigo6G-12, application\_type is different from the application\_type that the Ndigo6G-12 is currently configured in. That is, the FPGA is only reconfigured, if application type changes.

By setting force bitstream update to true, one can force a reconfiguration of the FPGA.

#### int partial\_bitstream\_size

Size of partial\_bitstream.

Reserved for future expandability.

## uint32\_t \*partial\_bitstream

Pointer to a buffer with partial bitstream data.

Can be nullptr if application\_type matches application\_type of currently installed firmware.

Reserved for future expandability.

#### const char \*firmware\_locations

Location where firmware is installed.

Pointer to a list of paths (separated by ;) Can be nullptr if application\_type matches application type of currently installed firmware.

#### 3.3 Status information

The driver provides functions to retrieve detailed information on the type of board, it's configuration, settings and state. The information is split according to its scope and the computational requirements to query the information from the board.

int ndigo6g12\_get\_driver\_revision()

Get the driver version in integer format.

#### **Returns**

The driver version in the same format as ndigo6g12\_static\_info::driver\_revision.

const char \*ndigo6g12\_get\_driver\_revision\_str()

Get the driver version in string format.

#### **Returns**

The Driver version including SVN build revision as a string with format x.y.z.svn.

int ndigo6g12\_count\_devices(int \*error\_code, const char \*\*error\_message)

Get the number of Ndigo6G-12 boards that are installed in the system.

#### **Parameters**

- error\_code [out] Pointer to an integer in which to store the error code.

- · error\_message [out] Location in which to store the error message as plain text.

#### **Returns**

The number.

int ndigo6g12\_get\_static\_info(ndigo6g12\_device \*device, ndigo6g12\_static\_info \*static\_info) Get the static information.

The static information does not change after the device initialization.

#### **Parameters**

- device [in] Pointer to the device from which to get the information.

- static\_info [out] Pointer to a structure in which to store the information.

#### **Returns**

See Function return values.

int ndigo6g12\_get\_param\_info(ndigo6g12\_device \*device, ndigo6g12\_param\_info \*param\_info) Get parametric information.

The parametric information may change due to the configuration.

#### **Parameters**

- · device [in] Pointer to the device from which to get the information.

- param\_info [out] Pointer to a structure in which to store the information.

#### **Returns**

See Function return values.

int ndigo6g12\_get\_fast\_info(ndigo6g12\_device \*device, ndigo6g12\_fast\_info \*fast\_info) Get fast status information.

The information can be retrieved within a few microseconds.

#### **Parameters**

- device [in] Pointer to the device from which to get the information.

- fast\_info [out] Pointer to a structure in which to store the information.

#### **Returns**

See Function return values.

int ndigo6g12\_get\_pcie\_info(ndigo6g12\_device \*device, crono\_pcie\_info \*pcie\_info)

Reads the PCIe info like correctable and uncorrectable errors.

#### **Parameters**

- · device [in] Pointer to the device.

- pcie\_info [out] Pointer to the structure in which to store the information.

#### **Returns**

See Function return values.

### struct ndigo6g12\_param\_info

Contains configuration changes.

Structure filled by *ndigo6g12\_get\_param\_info()*. This structure contains information that may change indirectly due to configuration changes.

#### **Public Members**

### double bandwidth

Bandwidth.

4.5 or 6.5 GHz depending on ndigo6g12\_configuration::extended\_bandwidth.

#### int resolution

ADC sample resolution.

Always 12 bit.

### double sample\_rate

Actual ADC sample rate of currently sampled data.

Depending on *ndigo6g12\_configuration::adc\_mode*, that is, sample\_rate = 6.4 GHz/*chan-nels*.

### double sample\_period

The period that one sample in the data represents in picoseconds.

### double tdc\_period

The period that one TDC bin in the data represents in picoseconds.

### double packet\_ts\_period

The period that one tick of the packet timestamp represents in picoseconds.

### uint64\_t tdc\_packet\_timestamp\_offset

The TDC packet timestamp offset.

Since TDC packets carry the timestamp of the end of the packet, to calculate the start, tdc packet timestamp offset has to be subtracted.

### uint32\_t tdc\_rollover\_period

Time span of one TDC timestamp rollover period in units of the TDC binsize.

All TDC hits within this period are written to one crono\_packet.

### double adc\_sample\_delay

The delay of the ADC samples relative to TDC timestamps in picoseconds.

Note: For driver release 2.2.0 with firmware 1.25086, this value is bugged.

### int board\_id

The ID the board uses to identify itself in the output data stream.

Takes values 0 to 255.

#### int channels

Number of ADC channels in the current mode.

See ndigo6g12\_configuration::adc\_mode.

### int channel\_mask

Mask with a set bit for each enabled input channel.

### int tdc\_channels

Number of TDC channels in the current mode.

### int64\_t total\_buffer

The total amount of the DMA buffer in bytes.

### int samples\_per\_clock

The number of samples in one clock cycle in the current mode.

### struct ndigo6g12\_static\_info

Structure contains static information.

This structure contains information about the board that does not change during run time. It is provided by ndigo6g12\_get\_static\_info().

#### **Public Members**

### char bitstream\_date[NDIGO6G12\_BITSTREAM\_DATE\_LEN]

Bitstream creation date.

DIN EN ISO 8601 string YYYY-MM-DD HH:DD:SS describing the time when the bitstream was created.

### int board\_configuration

Describes the schematic configuration of the board.

The same board schematic can be populated in multiple variants. This is a 8-bit code that can be read from a register.

### int board\_revision

Board revision number.

The board revision number can be read from a register. It is a four bit number that changes when the schematic of the board is changed.

- · 0: Experimental version of the first board. Labeled "Rev. 1".

- · 2: First commercial version. Labeled "Rev. 2"

### int board\_serial

The board's serial number.

With year and running number in 8.24 format (yy.nnn; 8 bits are used to encode the year, 24 bits to encode the number).

The number is identical to the one printed on the silvery sticker on the board.

### char calibration\_date[NDIGO6G12\_CALIBRATION\_DATE\_LEN]

Calibration date.

DIN EN ISO 8601 string YYYY-MM-DD HH:DD describing the time when the card was calibrated.

### int chip\_id

16-bit factory ID of the ADC chip.

This is the chipID as read from the 16-bit ADC chip-ID register.

### crono\_bool\_t dc\_coupled

Shows if the inputs are DC-coupled.

Default is false, that is, AC-coupled.

### int driver\_revision

Encoded version number for the driver.

The lower three bytes contain a triple-level hierarchy of version numbers. E.g., 0x010103 encodes version 1.1.3.

A change in the first digit generally requires a recompilation of user applications. Change in the second digit denote significant improvements or changes that don't break compatibility and the third digit changes with minor bugfixes and the like (see https://semver.org/).

### int driver\_build\_revision

The build number of the driver according to cronologic's internal versioning system.

### crono\_bool\_t flash\_valid

Calibration data read from flash is valid.

If not false, the driver found valid calibration data in the flash on the board and is using it.

### int fw\_revision

Revision number of the FPGA configuration.

### int fw\_type

Type of firmware, always 5 -> Ndigo6G-12.

### int pcb\_serial

Trenz serial number.

#### int svn\_revision

Subversion revision ID of the FPGA configuration.

A number to track builds of the firmware in more detail than the firmware revision. It changes with every change in the firmware, even if there is no visible effect for the user. The subversion revision number can be read from a register.

### int application\_type

Shows the initialized mode.

See NDIGO6G12\_APP\_TYPE\_\* constants.

### char config\_flash\_signature\_primary[NDIGO6G12\_FLASH\_SIG\_LEN]

Shows the signature of the primary flash.

### char config\_flash\_signature\_secondary[NDIGO6G12\_FLASH\_SIG\_LEN]

Shows the signature of the secondary flash.

### double auto\_trigger\_ref\_clock

Auto trigger clock frequency.

The clock frequency of the auto trigger in Hz used for the calculations of ndigo6g12\_configuration::auto\_trigger\_period.

Fixed at 200 MHz.

### struct ndigo6g12\_fast\_info

Contains fast dynamic information.

This structure is filled by *ndigo6g12\_get\_fast\_info()*. This information can be obtained within a few microseconds.

#### **Public Members**

#### int **state**

The current state of the device.

Is one of the following:

### NDIGO6G12\_DEVICE\_STATE\_INITIALIZED

Device is initialized but not yet configured for data capture.

### NDIGO6G12\_DEVICE\_STATE\_CONFIGURED

Device is ready for data capture.

### NDIGO6G12\_DEVICE\_STATE\_CAPTURING

Device has started data capture.

### int fan\_speed

Speed of the FPGA fan in rounds per minute.

Reports 0 if no fan is present.

### double fpga\_temperature

Temperature of the FPGA in °C.

### double fpga\_vccint

Internal Voltage of the FPGA in V. Useful debugging information.

### double fpga\_vccaux

Auxillary Voltage of the FPGA in V. Useful debugging information.

### double fpga\_vccbram

BRAM Voltage of the FPGA in V. Useful debugging information.

### double mgt\_0v9

Shows measured voltage for the mgt\_0v9 power supply in V. Useful debugging information.

### double mgt\_1v2

Shows measured Voltage for the mgt\_1v2 power supply in V. Useful debugging information.

### double adc\_2v5

Shows measured voltage for the 2v5 power supply in V. Useful debugging information.

### double clk\_3v3

Shows measured voltage for the clk\_3v3 power supply in V. Useful debugging information.

### double adc 3v3

Shows measured voltage for the adc\_3v3 power supply in V. Useful debugging information.

### double pcie\_3v3

Shows measured voltage for the pcie\_3v3 power supply in V. Useful debugging information.

### double opamp\_5v2

Shows measured voltage for the opamp\_5v2 power supply in V. Useful debugging information.

### double temp4633\_1

Shows temperature of voltage regulartor U3\_1 in °C.

### double temp4633\_2

Shows temperature of voltage regulator U3\_2 in °C.

### double temp4644

Shows temperature of voltage regulator U4 in °C.

### double tdc1\_temp

Temperature of the TDC-chip in °C.

### double ev12\_cmiref

Shows voltage for differential ADC input common mode voltage in V.

Measured or calibration target depending on board revision and assembly variant.

### double ev12\_temp

Temperature of the ADC in °C.

#### int alerts

Alert bits from temperature sensor and the system monitor.

Bit 0 is set if the TDC temperature exceeds 140°C. In this case the TDC shut down and the device needs to be reinitialized.

Is one of the following:

### NDIGO6G12\_ALERT\_FPGA\_TEMPERATURE

FPGA temperature alert (> 70°C)

### NDIGO6G12\_ALERT\_VCCINT

Internal FPGA voltage out of range (< 0.83 V or > 0.88 V).

### NDIGO6G12\_ALERT\_VCCAUX

FPGA auxiliary voltage out of range (< 1.75 V or > 1.89 V).

### NDIGO6G12 ALERT FPGA TEMPERATURE CRITICAL

FPGA temperature critical (> 80°C)

### NDIGO6G12\_ALERT\_THS\_TEMPERATURE\_CRITICAL

THS temperature critical (> 140°C)

### int pcie\_link\_width

Number of PCIe lanes the card uses.

Should always be 8 for the Ndigo6G-12.

### int pcie\_link\_speed

Data rate of the PCIe card.

Should always be 3 for the Ndigo6G-12.

### int pcie\_max\_payload

Maximum size for a single PCIe transaction in bytes.

Depends on the system configuration.

### crono\_bool\_t adc\_data\_pll\_locked

ADC data clock is PLL locked.

### crono\_bool\_t adc\_data\_pll\_lost\_lock

ADC data clock PLL lost lock (Sticky Bit).

### int adc\_lanes\_synced

Shows the synced ADC lanes.

Each bit corresponds to one lane. Useful debugging information.

### int adc\_lanes\_lost\_sync

Shows the ADC lanes that lost sync.

Each bit corresponds to one lane. Useful debugging information.

### int adc\_lanes\_fifo\_empty

Shows which ADC lanes have an empty FIFO.

Each bit corresponds to one lane. Useful debugging information.

### int adc\_lanes\_fifo\_full

Shows which ADC lanes have a full FIFO.

Each bit corresponds to one lane. Useful debugging information.

### int adc\_lanes\_running

Shows which ADC lanes are running.

Each bit corresponds to one lane. Useful debugging information.

### int adc\_lanes\_sync\_timeout

Shows which ADC lanes were unable to sync before a timeout.

Each bit corresponds to one lane. Useful debugging information.

### int adc\_sync\_retry\_count

The number of ADC lane synchronization retries.

Default is set to 0. Useful debugging information.

### int adc\_sync\_strobe\_retry\_count

The number of ADC strobe synchronization retries.

Default is set to 0. Useful debugging information.

### int adc\_sync\_delay\_count

16 Bit number showing when the last ADC lane synchronization was achieved.

Useful debugging information.

### crono\_bool\_t adc\_mgt\_power\_good

Shows if the supplied mgt power is sufficient.

Useful debugging information.

### ${\tt crono\_bool\_t~lmk\_pll1\_locked}$

Shows if lmk\_pll1 is locked. Useful debugging information.

#### crono\_bool\_t lmk\_pl12\_locked

Shows if Imk\_pll2 is locked. Useful debugging information.

### crono\_bool\_t lmk\_lost\_lock

Shows if lmk lost lock. Useful debugging information.

### int lmk\_lock\_wait\_count

Wait count of the lmk. Useful debugging information.

### int lmk\_ctrl\_vcxo

Usefull for hardware debugging.

### crono\_bool\_t lmx\_locked

Imx locked. Useful debugging information.

### crono\_bool\_t lmx\_lost\_lock

lmx lost lock. Useful debugging information.

Imx lock wait count. Useful debugging information.

### struct crono\_pcie\_info

Structure containing PCle information.

### **Public Members**

### uint32\_t pwr\_mgmt

Organizes power supply of PCIe lanes.

### uint32\_t link\_width

Number of PCIe lanes that the card uses.

Should be 1, 2, or 4 for Ndigo5G and 1, 2, 4, or 8 for the Ndigo6G-12. Ideally, should be the respective maximum.

### uint32\_t max\_payload

Maximum size in bytes for one PCIe transaction.

Depends on the system configuration.

### uint32\_t link\_speed

Data rate of the PCIe card.

Depends on the system configuration.

### uint32\_t error\_status\_supported

Different from 0 if the PCIe error status is supported for this device.

### uint32\_t correctable\_error\_status

Correctable error status flags, directly from the PCIe config register.

Useful for debugging PCIe problems. 0, if no error is present, otherwise one of CRONO\_PCIE\_\*

### uint32\_t uncorrectable\_error\_status

Uncorrectable error status flags, directly from the PCIe config register.

Useful for debugging PCIe problems. 0, if no error is present, otherwise one of CRONO\_PCIE\_UNC\_\*.

### uint32\_t reserved

For future extension.

## 3.4 Configuration

The Ndigo6G-12 board is configured with a configuration structure (ndigo6g12\_configuration).

The user should first obtain a standard set of configuration parameters using ndigo6g12 get default configuration(), then modify only the necessary parameters to their specific needs.

The configuration itself is done by calling <a href="mailto:ndigo6g12\_configure">ndigo6g12\_configure</a> ().

int ndigo6g12\_get\_default\_configuration(ndigo6g12\_device \*device, ndigo6g12\_configuration \*config)

Copies the default configuration to the specified config pointer.

Default values of ndigo6g12\_configuration:

- · adc mode =

- NDIGO6G12\_ADC\_MODE\_A (if application\_type = NDIGO6G12\_APP\_TYPE\_1CH)

- NDIGO6G12\_ADC\_MODE\_AD (if application\_type = NDIGO6G12\_APP\_TYPE\_2CH)

- NDIGO6G12\_ADC\_MODE\_ABCD (if application\_type = NDIGO6G12\_APP\_TYPE\_4CH)

- NDIGO6G12\_ADC\_MODE\_A (if application\_type = NDIGO6G12\_APP\_TYPE\_AVRG)

- adc cal set = 3

- analog\_offsets[i] = 0

- tdc\_trigger\_offsets[i] = NDIGO6G12\_DC\_OFFSET\_N\_NIM

- trigger[i]:

- edge = true

- rising = false

- threshold = 512

- trigger\_block[i]:

- enabled = false

- retrigger = false

- multi shot count = 1

- precursor = 0

- *length* = 16

- sources = NDIGO6G12\_TRIGGER\_SOURCE\_0

- gates = NDIGO6G12\_TRIGGER\_GATE\_NONE

- minimum\_free\_packets = 0

- gating\_block[i]:

- negate = false

- retrigger = false

- start = 0

- stop = 1000

- sources = NDIGO6G12\_TRIGGER\_SOURCE\_0

- tdc\_configuration:

- channel[i]:

- \* enable = false

- \* gating\_block:

- · enable = false

- · negate = false

- · retrigger = false

- retrigger = NDIGO6G12\_TRIGGER\_SOURCE\_AUTO

- start = 0

- · *stop* = 1000

- sources = NDIGO6G12\_TRIGGER\_SOURCE\_0

- \* tiger\_block:

- · mode = NDIGO6G12\_TIGER\_OFF

- · negate = true

- · retrigger = false

- retrigger = NDIGO6G12\_TRIGGER\_SOURCE\_AUTO

- start = 0

- $\cdot$  stop = 1

- sources = NDIGO6G12\_TRIGGER\_SOURCE\_0

- skip\_alignment = false

- alignment\_mode = false

- alignment\_pin\_high\_z = false

- alignment\_pin\_invert = false

- alignment\_phase\_steps = 6

- send\_empty\_packets = false

- auto\_trigger\_period = 200000

- auto\_trigger\_random\_exponent = 0

- output\_mode =

- NDIGO6G12\_OUTPUT\_MODE\_SIGNED32 (if application\_type = NDIGO6G12\_APP\_TYPE\_AVRG

- NDIGO6G12\_OUTPUT\_MODE\_SIGNED16 (otherwise)

- extended\_bandwidth = false

ramp\_test\_mode = false

#### **Parameters**

- device [in] Pointer to the device from which to get the information.

- · config [out] Pointer to a structure in which to store the configuration values.

#### **Returns**

See Function return values.

int ndigo6g12\_configure(ndigo6g12\_device \*device, ndigo6g12\_configuration \*config)

Configures the Ndigo6G-12 device.

The config information is copied such that it can be changed after the call to ndigo6g12\_configure.

#### **Parameters**

- device [in] Pointer to the device from which to get the information.

- config [out] Pointer to the configuration structure.

#### Returns

See Function return values.

### struct ndigo6g12\_configuration

Structure that contains the configuration values for the Ndigo6G-12.

This structure contains the configuration information. It is used in conjunction with ndigo6g12\_get\_default\_configuration() and ndigo6g12\_configure().

### **Public Members**

### int adc\_mode

Configure ADC mode.

The chosen ADC mode has to be supported by the current NDIGO6G12\_APP\_TYPE.

For example, if NDIG06G12 APP TYPE 1CH is used, one cannot choose, e.g., adc mode = NDIGO6G12 ADC MODE AA, but one has to either choose NDIGO6G12 ADC MODE A or NDIGO6G12\_ADC\_MODE\_D.

Default value depends on ndigo6g12\_init\_parameters::application\_type.

- NDIGO6G12\_APP\_TYPE\_4CH: NDIGO6G12\_ADC\_MODE\_A

- NDIGO6G12\_APP\_TYPE\_2CH: NDIGO6G12\_ADC\_MODE\_AD

- NDIGO6G12\_APP\_TYPE\_1CH: NDIGO6G12\_ADC\_MODE\_ABCD

For more information, see Section 2.1.

Must be one of the following:

### NDIGO6G12\_ADC\_MODE\_ABCD

4-channel mode at 1600 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_AADD

4-channel mode at 1600 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_AAAA

4-channel mode at 1600 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_DDDD

4-channel mode at 1600 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_AD

2-channel mode at 3200 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_AA

2-channel mode at 3200 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_DD

2-channel mode at 3200 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_A

1-channel mode at 6400 Msps sample rate

### NDIGO6G12\_ADC\_MODE\_D

1-channel mode at 6400 Msps sample rate

### int adc\_cal\_set

Select ADC calibration set.

Default is 3. Do not change.

### double analog\_offsets[NDIGO6G12\_ADC\_CHANNEL\_COUNT]

Set the offsets of the ADC inputs in V.

The indices 0 to 3 of the array correspond to ADC channels A to D.

Must be between  $\pm$  0.5 V.

Defaults are 0 V for each ADC channel.

### double tdc\_trigger\_offsets[NDIGO6G12\_TDC\_CHANNEL\_COUNT]

Set DAC for trigger threshold of the TDC inputs in V.

Channel assignment:

- 0 to 3: high-resolution TDC, inputs E to H

- · 4 and 5: inputs TRG and GATE

Set to a value between -1.32 V and +2.0 V.

This should be close to 50% of the height of your pulses on the inputs. Examples for various signaling standards are defined below. The inputs are AC coupled. This means that for pulse inputs the absolute voltage is not important. Only the relative pulse amplitude causes the input circuits to switch. tdc\_trigger\_offset for an input must be set to the relative switching voltage for the input standard in use. If the pulses are negative, a negative switching threshold must be set and vice versa.

Defaults are NDIGO6G12\_DC\_OFFSET\_N\_NIM for each TDC channel.

Defines for various signal standards:

NDIGO6G12\_DC\_OFFSET\_P\_NIM

NDIGO6G12\_DC\_OFFSET\_P\_CMOS

NDIGO6G12\_DC\_OFFSET\_P\_LVCMOS\_33

NDIGO6G12\_DC\_OFFSET\_P\_LVCMOS\_25

NDIGO6G12\_DC\_OFFSET\_P\_LVCMOS\_18

NDIGO6G12\_DC\_OFFSET\_P\_TTL

NDIGO6G12\_DC\_OFFSET\_P\_LVTTL\_33

NDIGO6G12\_DC\_OFFSET\_P\_LVTTL\_25

NDIGO6G12\_DC\_OFFSET\_P\_SSTL\_3

NDIGO6G12\_DC\_OFFSET\_P\_SSTL\_2

NDIGO6G12\_DC\_OFFSET\_N\_NIM

NDIGO6G12\_DC\_OFFSET\_N\_CMOS

NDIGO6G12\_DC\_OFFSET\_N\_LVCMOS\_33

NDIGO6G12\_DC\_OFFSET\_N\_LVCMOS\_25

NDIGO6G12\_DC\_OFFSET\_N\_LVCMOS\_18

NDIGO6G12\_DC\_OFFSET\_N\_TTL

NDIGO6G12\_DC\_OFFSET\_N\_LVTTL\_33

NDIGO6G12\_DC\_OFFSET\_N\_LVTTL\_25

```

NDIGO6G12_DC_OFFSET_N_SSTL_3

```

NDIGO6G12\_DC\_OFFSET\_N\_SSTL\_2

### ndigo6g12\_trigger trigger[NDIGO6G12\_TRIGGER\_COUNT]

Configuration of the external trigger sources.

The entries in the array correspond to the following defines.

ndigo6g12\_trigger::threshold is ignored for index NDIGO6G12\_TRIGGER\_TDC0 and above.

ndigo6g12\_trigger::edge and ndigo6g12\_trigger::rising are ignored for indeces NDIGO6G12\_TRIGGER\_AUTO and NDIGO6G12\_TRIGGER\_ONE.

NDIGO6G12\_TRIGGER\_AO

NDIGO6G12\_TRIGGER\_A1

NDIGO6G12\_TRIGGER\_BO

NDIGO6G12\_TRIGGER\_B1

NDIGO6G12\_TRIGGER\_CO

NDIGO6G12\_TRIGGER\_C1

NDIGO6G12\_TRIGGER\_DO

NDIGO6G12\_TRIGGER\_D1

NDIGO6G12\_TRIGGER\_TDC0

NDIGO6G12\_TRIGGER\_TDC1

NDIGO6G12\_TRIGGER\_TDC2

NDIGO6G12\_TRIGGER\_TDC3

NDIGO6G12\_TRIGGER\_TRG

NDIGO6G12\_TRIGGER\_GATE

NDIGO6G12\_TRIGGER\_AUTO

### NDIGO6G12 TRIGGER ONE

### NDIGO6G12\_TRIGGER\_FPGAO

Deprecated. Alias for NDIGO6G12\_TRIGGER\_TRG.

### NDIGO6G12\_TRIGGER\_FPGA1

Deprecated. Alias for NDIGO6G12\_TRIGGER\_GATE.

### ndigo6g12\_trigger\_block trigger\_block[NDIGO6G12\_ADC\_CHANNEL\_COUNT]

Trigger settings of ADC inputs.

The number of input channels depends on ADC mode.

### ndigo6g12\_gating\_block gating\_block[NDIGO6G12\_GATE\_COUNT]

Configuration of gating blocks.

Gating blocks are used to filter trigger.

### ndigo6g12\_tdc\_configuration tdc\_configuration

Configuration of TDC channels.

### ndigo6g12\_averager\_configuration average\_configuration

Configuration of the Averager.

### int auto\_trigger\_period

Component to create a trigger either periodically or randomly.

To be exact, there are two parameters  $M = auto\_trigger\_period$  and  $N = auto\_trigger\_ran$ dom\_exponent that result in a distance between triggers of  $T = M + [1...2^N] - 1$  clock cycles, where  $6 \le M < 2^{32}$  and  $0 \le N < 32$ .

There is no enable or reset as the usage of this trigger can be configured in the channels. Each clock cycle is 5 ns.

Default is 200000, corresponding to a 1 kHz auto trigger.

### int auto\_trigger\_random\_exponent

Component to create a trigger either periodically or randomly.

See auto\_trigger\_period.

Default is 0.

### int output\_mode

Output mode of the ADC data.

Default value depends on ndigo6g12\_init\_parameters::application\_type.

- NDIGO6G12\_APP\_TYPE\_AVRG: NDIGO6G12\_OUTPUT\_MODE\_SIGNED32

- otherwise: NDIGO6G12\_OUTPUT\_MODE\_SIGNED16.

Must be one of the following:

### NDIGO6G12 OUTPUT MODE RAW

Return the native range (0 to 4095) augmented by two ADC control bits per sample.

Not supported for user applications.

### NDIGO6G12\_OUTPUT\_MODE\_SIGNED16

Return a signed 16 integer.

The range is -32768 to 32767.

### NDIGO6G12\_OUTPUT\_MODE\_SIGNED32

Output in signed32 integer format.

Must be used in (and only in) averaging mode. The range is  $-2^{31}$  to  $2^{31} - 1$ .

### NDIGO6G12\_OUTPUT\_MODE\_RAW\_NO\_CB

Return the native range (0 to 4095).

For more information, see Section 4.3.

### crono\_bool\_t extended\_bandwidth

Extended bandwidth.

If true, the input bandwidth is 6.5 GHz instead of the default 4.5 GHz.

Since the extended input bandwidth of the ADC influences the total bandwidth of the Ndigo6G-12 board only in a minimal manner, we recommend using the non-extended input bandwidth of 4.5 GHz. This ensures the best signal-to-noise ratio.

Default is false.

### crono\_bool\_t ramp\_test\_mode

Default is false. Do not change.

### crono\_bool\_t sample\_averaging

Calculate sample average for multi-sampling modes AAAA, DDDD, AADD, AA, and DD.

Manipulate the output in multi-sampling modes.

- true: Average all samples and combine them to a single output.

- · false: Output all samples in their own package.

For more information, see Multiple Sampling Modes in Section 2.1.

### struct ndigo6g12\_trigger

Structure that contains trigger settings.

#### **Public Members**

#### short threshold